NXP Semiconductors SJA1124 Quad LIN Master Transceiver

NXP Semiconductors SJA1124 Quad Local Interconnect Network (LIN) Master Transceiver contains a LIN master controller and LIN transceiver with master termination in each channel. This device transfers LIN master frames to the physical LIN bus via the LIN physical layer. NXP SJA1124 LIN master transceiver is designed for in-vehicle subnetworks using baud rates up to 20kBd. This LIN master channel device complies with LIN 2.0, LIN 2.1, LIN 2.2, and LIN 2.2A. An SPI interface and an interrupt output provide the interface between the SJA1124 and a microcontroller.SJA1124 converts transmit data streams received on the SPI into LIN master frames transmitted on the LIN bus. The LIN master frames are transmitted as optimized bus signals shaped to minimize electromagnetic emission (EME). The SJA1124 can be woken up via the LIN pins and the SPI interface in Low Power mode.

Features

- Four LIN master channels

- LIN master controller

- LIN transceiver

- LIN master termination consisting of a diode and a 1kΩ ±10% resistor

- Compliant with

- LIN 2.0, LIN 2.1, LIN 2.2, and LIN 2.2A

- ISO 17987-3:2016 and ISO 17987-4:2016 (12V LIN)

- SAE J2602-1

- Very low current consumption in Low Power mode with wake-up via SPI or LIN

- Option to control an external voltage regulator via the INHN output

- Bus signal shaping optimized for baud rates up to 20kBd

- SPI for communicating with the microcontroller

- Interrupts can be configured individually

- Facilitates synchronous LIN frame transmission across multiple SJA1124 devices

- VIO input for direct interfacing with 3.3V and 5V microcontrollers

- On-chip phase-locked loop (PLL) for LIN master controller

- Passive behavior in the unpowered state

- Undervoltage detection

- Leadless DHVQFN24 package (3.5mm × 5.5mm) supporting improved Automated Optical Inspection (AOI) capability

- LIN master controllers

- Independent per LIN channel

- Baud rate

- Operating mode

- Status and interrupt

- Complete LIN frame handling and transfer

- One interrupt per LIN frame

- Slave response timeout detection

- Programmable break length

- Automatic sync field generation

- Programmable stop bit length

- Hardware parity generation

- Hardware or software checksum generation

- Fault confinement

- Fractional baud rate generator

- Independent per LIN channel

- Protection schemes

- Excellent electromagnetic immunity (EMI)

- ±6kV ESD protection according to IEC61000-4-2 for pins LIN1 to LIN4 and BAT

- Bus terminal and battery pin protected against transients in the automotive environment (ISO 7637)

- Bus terminal short-circuit proof to battery and ground

- LIN dominant timeout function

- Thermal protection

Block Diagram

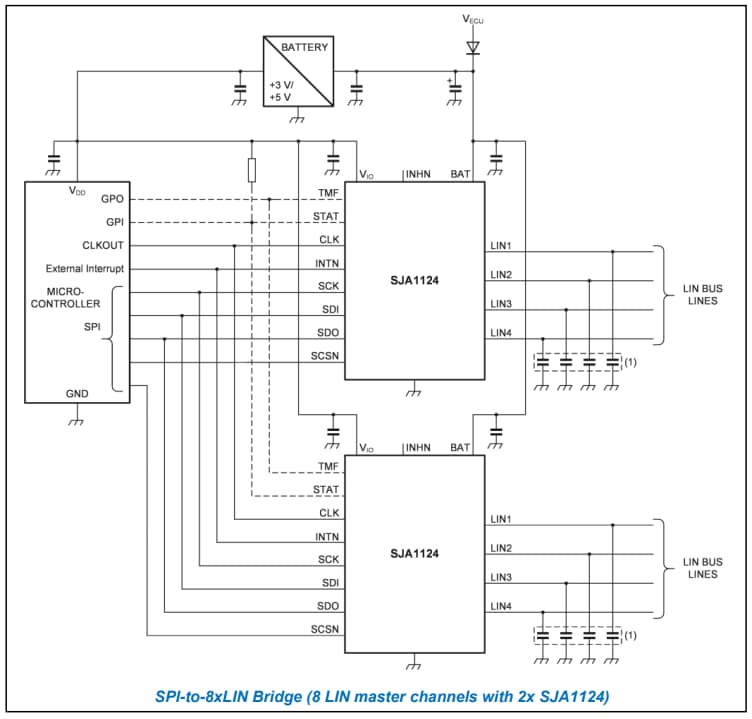

Application Circuit Diagram

Videos

Additional Resources

Published: 2018-12-09

| Updated: 2025-02-07